# シングルコア向け排他制御記述を含む RTOS利用システムのフルハードウェア化

Synthesis of Full Hardware of RTOS-Based Systems including Exclusion-Control Description for Single-Core

篠原 由季乃 Yukino Shinohara 大迫 裕樹 \*

石浦 菜岐佐

Yuuki Oosako Nagisa Ishiura

関西学院大学 理工学部 School of Science and Technology, Kwansei Gakuin University

#### 1 はじめに

組込みシステムの高機能化・複雑化に伴い、システムのリアルタイム性の実現は難しい課題となっている. RTOS (Real Time Operating System) を用いたシステムの応答性を向上させる一手法として、RTOS の機能およびタスク/ハンドラの全てをハードウェア化する手法 [1] が提案されている. 本稿では、この手法の排他制御記述に関する制約を緩和し、シングルコア向け排他制御記述を含むシステムに対応する手法を提案する.

## 2 RTOS 利用システムのフルハードウェア実装

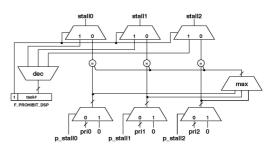

文献 [1] では、TOPPERS/ASP3 上で動作するプログラムを入力として、これを実行する CPU と機能等価なハードウェア (構成を図 1 に示す)を自動生成している。 $T0\sim T2$  はタスク、IH は割り込みハンドラに対応する回路であり、実行可能になれば優先順位に関わらず全て並列に実行される。 manager は各タスク/ハンドラおよびシステムの状態をステータスレジスタに保持し、その値から決定される stall 信号 (実行の時 stall=0、停止の時 stall=1) により各タスク/ハンドラの実行を制御する。

タスクが並列実行されるため、この手法では mutex を用いた排他制御記述を前提としている。しかし、シングルコアのシステムではディスパッチ/割り込みの禁止や優先度の引き上げにより排他制御を記述することがあり、このようなプログラムを合成することはできない。

図 1 合成されるハードウェアの構成

## 3 シングルコア向けの排他制御記述への対応

本稿では, 文献 [1] の手法にディスパッチ禁止/割り込み禁止の機能, および優先度最大のタスクのみが実行されるモードを追加する.

## (1) ディスパッチ禁止/割り込み禁止の実装

あるタスクがディスパッチ禁止のコールを呼ぶと、解除のコールが呼ばれるまでそのタスクのみが実行されるようにする。これは、manager 内の F\_PROHIBIT\_DSP ワードにディスパッチ禁止ビットとそのタスクの番号を書き込み、図 2 のような回路でそのタスクへの stall のみを解除することにより実現する。割り込み禁止は、割り込み禁止フラグがセットされている間はハンドラの stallを解除しないことにより実現する。

(2) 優先度最高のタスクのみ実行 実行可能なタスクのうち優先度最高のタスクのみ stall

図 2 stall 信号生成回路

を解除するように manager を変更する. これは図 2のような回路で実行可能タスクの最大優先度を求め (p\_stalliは元々の stall 信号である), 優先度がそれに一致するタスクのみ stall を解除することにより実現する.

## 4 実験結果

提案手法に基づいて, manager を Verilog HDL で設計した. ディスパッチ/割り込み禁止のサービスコールを C 言語で記述し, TOPPERS/ASP3 付属のサンプルプログラム "sample1" を合成した. 高位合成システムには ACAP [2] を用い, 論理合成は Xilinx Vivado (2016.4) により Artix-7 をターゲットに行なった.

合成結果を表 1 に示す. (a) は各モジュールの LUT数, (b) は各サービスコールが呼ばれてから状態が更新されるまでのサイクル数である. 全体の回路規模が大きいため提案手法の影響は小さい. ディスパッチ/割り込みの禁止/許可が 13 サイクル以内に実行できている.

表 1 合成結果

| (a) 回路規模  |                   |                   |

|-----------|-------------------|-------------------|

|           | 本研究               | 文献 [1]            |

| module    | $\# \mathrm{LUT}$ | $\# \mathrm{LUT}$ |

| manager   | 3877              | 5305              |

| MAIN_TASK | 5463              | 5382              |

| EXC_TASK  | 4292              | 4703              |

| TASK1     | 5564              | 5320              |

| TASK2     | 6827              | 6620              |

| TASK3     | 6314              | 6258              |

| total     | 32337             | 33588             |

| service call              | #cycle |  |

|---------------------------|--------|--|

| dis_dsp                   | 12     |  |

| $ena\_dsp$                | 13     |  |

| $\operatorname{dis\_int}$ | 13     |  |

| ena_int                   | 13     |  |

## 5 むすび

本稿では, 文献 [1] の手法をシングルコア向け排他制御記述に対応させる手法を提案した. 回路規模の削減が今後の課題である.

謝辞 本研究は一部 JSPS 科研費 19H04081 の助成による.

## 参考文献

- [1] Y. Oosako, N. Ishiura, H. Tomiyama, and H. Kanbara: "Synthesis of full hardware implementation of RTOS-based systems," in *Proc. RSP 2018*, pp. 1–7 (Oct. 2018).

- [2] N. Ishiura, H. Kanbara, and H. Tomiyama: "ACAP: Binary synthesizer based on MIPS object codes," in *Proc. ITC-CSCC 2014*, pp. 725–728 (July 2014).